# <u>APIO16</u>

## Radiation Hardened level translating I<sup>2</sup>C, SMBUS, SPI I/O expander

### **1 GENERAL DESCRIPTION**

The **APIO16** is a radiation-hardened by design **level translating I<sup>2</sup>C, SMBUS, SPI I/O expander** that is ideally suited for space, medical imaging and other applications demanding radiation tolerance and high reliability. It is fabricated in a BiCMOS process utilizing proprietary radiation-hardening techniques, delivering high resiliency to single-event effects (SEE) and to a total ionizing dose (TID) as might be found in a Low Earth Orbit (LEO) environment.

Class 2 ESD protection on all inputs and outputs.

The APIO16 features extensive circuit techniques throughout, including triple modular redundancy, self correcting digital circuits and Dual Interlocked storage CEll (DICE) latches to ensure a high level of immunity to single-event transients (SET) and single event upset (SEU) without requiring additional redundant devices.

For more demanding radiation tolerance, see Geosynchronous Earth Orbit (GEO) version **AFIO16**

#### 1.1 FEATURES

- 16-bit general purpose I/O expander

- MODE pin selects between SPI and  $I^2C\ /\ SMBUS$  operation

- I<sup>2</sup>C: 16 addresses, pin configurable: allows up to 16 APIO16 devices to share the same I<sup>2</sup>C bus

- SPI mode has 3 Chip select pins allowing built in address decoding

- 1.4 VDC to 5.5 VDC operation

- Extended operating temperature range (-55 °C to +125 °C)

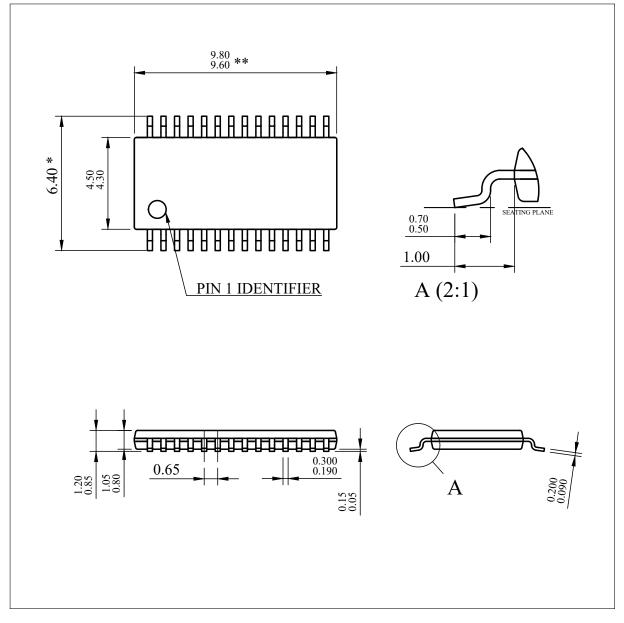

- Package: 28pin TSSOP

- Open drain INTB pin to alert controller when inputs change

- Level translation, seperate power pins for I/O ports and serial interface

- Schmitt trigger on all port inputs

- Schmitt trigger on serial interface inputs and filter when in  $\mathsf{l}^2\mathsf{C}$  mode

- 1 MHz Fast mode plus I<sup>2</sup>C, 25 MHz SPI

- Input/Output Configuration register

- Polarity Inversion register

- Internal power-on reset, no glitch on power-up

- Cold spareable I/Os

- Latched outputs with **21mA** sink and source drive

- Built-in triple redundancy for enhanced reliability

- Class 2 ESD protection (4000 V HBM, 500 V CDM)

- TID resilience: 56 krad (Si)

- SEL/SEU/SEFI resilience: LET of **77 MeV-cm<sup>2</sup>/mg**

### **APIO16**

DATASHEET

### PRELIMINARY DATASHEET Rad-Hard I/O expander

### CONTENTS

| 1 | <b>Gen</b><br>1.1                                            | eral Description<br>Features                                                                                                                                                                                                                                         | <b>1</b><br>1                                                                                                                                                               |             |

|---|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2 | Acro                                                         | onyms and Abbreviations                                                                                                                                                                                                                                              | 3                                                                                                                                                                           |             |

| 3 | Pin                                                          | Configuration                                                                                                                                                                                                                                                        | 4                                                                                                                                                                           |             |

| 4 | <b>Elec</b><br>4.1<br>4.2<br>4.3                             | 1 0                                                                                                                                                                                                                                                                  | <b>6</b><br>6<br>7<br>8                                                                                                                                                     |             |

| 5 | Турі                                                         | ical Characteristics                                                                                                                                                                                                                                                 | 13                                                                                                                                                                          |             |

| 6 | Deta<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8 | RESETBPOR VCCPMODEPortsINTBI^2 C operation $6.8.1$ I <sup>2</sup> C timing diagrams $6.8.2$ I <sup>2</sup> C write $6.8.3$ I <sup>2</sup> C read $6.8.4$ I <sup>2</sup> C read from portSPI operation $6.9.1$ SPI timing diagrams $6.9.2$ SPI write $6.9.3$ SPI read | 14           14           15           15           15           15           16           18           20           21           22           23           23           23 | 7<br>8<br>9 |

|   |                                                              | 6.9.4 SPI read 4-wire                                                                                                                                                                                                                                                | 23                                                                                                                                                                          | 1(          |

|   | Revi<br>Lega | sion Hi        | story                            | 34<br>35 |

|---|--------------|----------------|----------------------------------|----------|

| 8 |              | -              | formation                        | 33       |

|   | Pack         | aging          | Information                      | 32       |

|   |              | 6.13.9         | Extremely long transactions      | 31       |

|   |              | 6.13.8         | SPI loss of synchrony            | 31       |

|   |              | 6.13.7         | SPI illegal command              | 30       |

|   |              | 6.13.6         |                                  | 30       |

|   |              | 6.13.5         | I <sup>2</sup> C stop detect     | 30       |

|   |              | 0.1011         | fail                             | 30       |

|   |              | 6.13.4         |                                  | 50       |

|   |              | 6.13.3         |                                  | 30       |

|   |              | 6.13.2         | I <sup>2</sup> C illegal command | 30<br>30 |

|   | 6.13         | 6.13.1         | handling                         | 30<br>30 |

|   | 6.12         |                | guidelines                       | 30       |

|   | 6.40         |                | plex many devices in SPI mode    | 30       |

|   |              | 6.11.5         | <b>o</b> , , ,                   |          |

|   |              | 6.11.4         |                                  | 29       |

|   |              |                | SDA and SCLK for $I^2C$          | 28       |

|   |              | 6.11.3         |                                  |          |

|   |              |                | age bank                         | 27       |

|   |              | 6.11.2         |                                  |          |

|   | 0.11         |                | Basic I <sup>2</sup> C operation | 27       |

|   | 6.11         |                | ation circuit                    | 24       |

|   | 6.10         |                | SPI read from port               | 24<br>24 |

|   |              | 6.9.5<br>6.9.6 | SPI read 3-wire                  | 23<br>24 |

|   |              | 6 O F          | SDL road 2 wire                  | 22       |

### LIST OF TABLES

| 1  | Device Pinout                                          | 5  |

|----|--------------------------------------------------------|----|

| 2  | Absolute Maximum Ratings                               | 6  |

| 3  | Recommended Operating Conditions                       | 7  |

| 4  | Thermal Information                                    | 7  |

| 5  | Electrical Characteristics: general                    | 8  |

| 6  | Electrical Characteristics: general                    | 9  |

| 7  | Electrical Characteristics: general                    | 10 |

| 8  | Electrical Characteristics: I <sup>2</sup> C/SMBUS op- |    |

|    | eration                                                | 11 |

| 9  | Electrical Characteristics: SPI operation .            | 12 |

| 10 | I <sup>2</sup> C address                               | 17 |

| 11 | Device Pinout                                    | 24 |

|----|--------------------------------------------------|----|

| 12 | Input port 0 register                            | 24 |

| 13 | Input port 1 register                            | 24 |

| 14 | Output port 0 register                           | 25 |

| 15 | Output port 1 register                           | 25 |

| 16 | Polarity port 0 register                         | 25 |

| 17 | Polarity port 1 register                         | 25 |

| 18 | Configuration port 0 register                    | 25 |

| 19 | Configuration port 1 register                    | 26 |

| 20 | Standard I <sup>2</sup> C bus speed requirements | 28 |

| 21 | Ordering Information                             | 33 |

### DATASHEET **LIST OF FIGURES**

| 1 | block diagram                                            | 14 |

|---|----------------------------------------------------------|----|

| 2 | simplified port pin schematic                            | 16 |

| 3 | I <sup>2</sup> C timing diagram for single write oper-   |    |

|   | ation                                                    | 18 |

| 4 | I <sup>2</sup> C timing diagram for two write operations | 18 |

| 5 | I <sup>2</sup> C port read timing specifications         | 18 |

| 6 | I <sup>2</sup> C timing diagram for I2C specifications . | 19 |

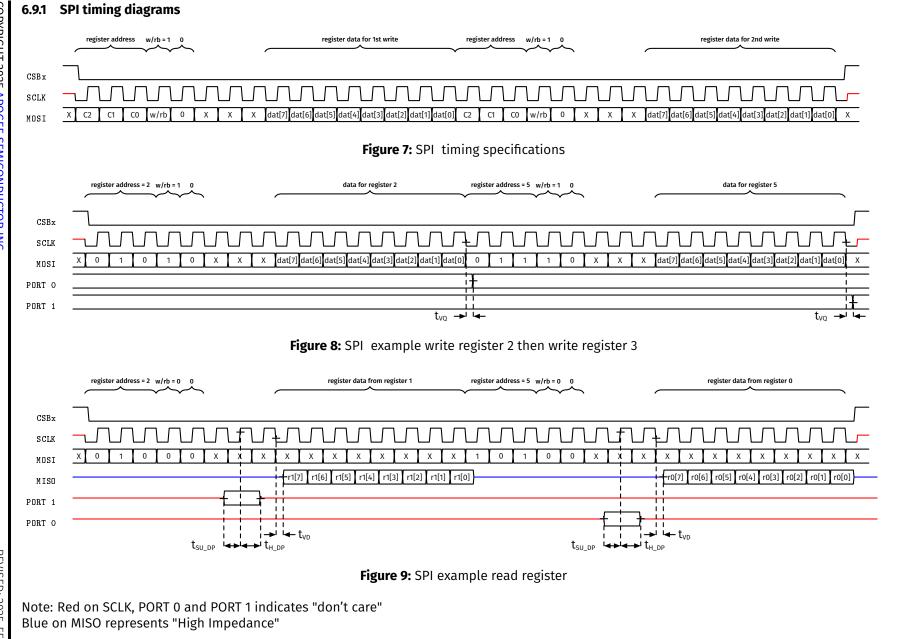

| 7 | SPI timing specifications                                | 22 |

|   |                                                          |    |

| 8  | SPI example write register 2 then write |    |

|----|-----------------------------------------|----|

|    | register 3                              | 22 |

| 9  | SPI example read register               | 22 |

| 10 | basic I <sup>2</sup> C application      | 27 |

| 11 | basic SPI application                   | 29 |

| 12 | Package Mechanical Drawing              | 32 |

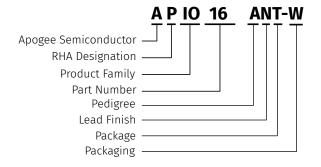

| 13 | Part Number Decoder                     | 33 |

### **2 ACRONYMS AND ABBREVIATIONS**

| ESD  | Electrostatic Discharge           |

|------|-----------------------------------|

| RHA  | Radiation Hardness Assurance      |

| SEFI | Single Event Functional Interrupt |

| SET  | Single Event Transient            |

| TMR  | Triple Modular Redundancy         |

| HBM  | Human-body Model                  |

POR Power On Reset SEE

Single Event Effects SEL

Single Event Latchup

Total Ionizing Dose TID CDM Charged-device Model

**API016**

PRELIMINARY DATASHEET Rad-Hard I/O expander

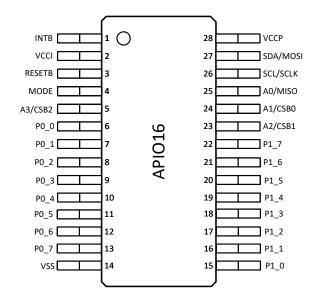

### **3 PIN CONFIGURATION**

#### Table 1: APIO16 device pinout description

| PIN NAME(S) | PIN NUMBER(S) |                             | DESCRIPTION                                                                                                                |  |  |

|-------------|---------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

|             |               | MODE=low (I <sup>2</sup> C) | MODE=hi (SPI)                                                                                                              |  |  |

| SCL/SCLK    | 26            | I <sup>2</sup> C SCL        | SPI SCLK input                                                                                                             |  |  |

| SDA/MOSI    | 27            | I <sup>2</sup> C SDA        | SPI MOSI input                                                                                                             |  |  |

| A3/CSB2     | 5             | address bit A3              | active low chip select CSB2                                                                                                |  |  |

| A2/CSB1     | 23            | address bit A2              | active low chip select CSB1                                                                                                |  |  |

| A1/CSB0     | 24            | address bit A1              | active low chip select CSB0                                                                                                |  |  |

| A0/MISO     | 25            | address bit A0              | MISO tri-state output                                                                                                      |  |  |

| INTB        | 1             |                             | active low interrupt output, pull up to a 5.5V maxi-<br>nrough a pull-up resistor                                          |  |  |

| RESETB      | 3             | active low                  | reset input pull up to VCCI if not required                                                                                |  |  |

| MODE        | 4             |                             | if low, part operates with an I <sup>2</sup> C interface, if high, part operates with an SPI interface. Tie to VSS or VCCI |  |  |

| VCCI        | 2             |                             | age for all pins other than ports                                                                                          |  |  |

| P0_0        | 6             | port 0 inpu                 | t/output 0                                                                                                                 |  |  |

| P0_1        | 7             | port 0 inpu                 | port 0 input/output 1                                                                                                      |  |  |

| P0_2        | 8             | port 0 inpu                 | port 0 input/output 2                                                                                                      |  |  |

| P0_3        | 9             | port 0 inpu                 | oort 0 input/output 3                                                                                                      |  |  |

| P0_4        | 10            | port 0 inpu                 | t/output 4                                                                                                                 |  |  |

| P0_5        | 11            | port 0 inpu                 | •                                                                                                                          |  |  |

| P0_6        | 12            | port 0 inpu                 | t/output 6                                                                                                                 |  |  |

| P0_7        | 13            | port 0 inpu                 | t/output 7                                                                                                                 |  |  |

| VSS         | 14            | ground                      |                                                                                                                            |  |  |

| P1_0        | 15            | port 1 inpu                 | t/output 0                                                                                                                 |  |  |

| P1_1        | 16            | port 1 inpu                 | •                                                                                                                          |  |  |

| P1_2        | 17            | port 1 inpu                 | •                                                                                                                          |  |  |

| P1_3        | 18            | port 1 inpu                 | •                                                                                                                          |  |  |

| P1_4        | 19            | port 1 inpu                 | •                                                                                                                          |  |  |

| P1_5        | 20            | port 1 inpu                 | •                                                                                                                          |  |  |

| P1_6        | 21            | port 1 inpu                 | •                                                                                                                          |  |  |

| P1_7        | 22            | port 1 inpu                 | •                                                                                                                          |  |  |

| VCCP        | 28            | supply volt                 | age for ports                                                                                                              |  |  |

| <b>APIO16</b> |

|---------------|

| DATASHEET     |

### **4 ELECTRICAL CHARACTERISTICS**

The sign convention for current follows JEDEC standards with negative values representing current sourced from the device and positive values representing current sunk into the device.

### 4.1 ABSOLUTE MAXIMUM RATINGS

Excursions beyond the values listed in Table 2 may cause permanent damage to the device. Proper function of the device cannot be guaranteed if these values are exceeded, and long-term device reliability may be affected. Functionality of the device at these values, or beyond those listed in Recommended Operating Conditions (Table 3) is not guaranteed.

All parameters are specified across the entire operating temperature range unless otherwise specified.

| SYMBOL                              | PARAMETER                                                                                                                                                                                                 |     | VALUE        | UNITS |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|-------|

| V <sub>CCI</sub> , V <sub>CCP</sub> | Supply voltage                                                                                                                                                                                            |     | -0.3 to +5.5 | V     |

| Vı                                  | INTB, RESETB, MODE, A3_CSB2,P0_1, P0_2,<br>P0_3, P0_4, P0_5, P0_6, P0_7, P1_1, P1_2, P1_3,<br>P1_4, P1_5, P1_6, P1_7, A2/CSB1, A1/CSB0,<br>A0/MISO, SCL/SCLK, SDA/MOSI<br>maximum current into input pins |     | -0.3 to +5.5 | V     |

| I <sub>IK</sub>                     | maximum current into input pins                                                                                                                                                                           |     | -100 to 100  | mA    |

| l <sub>o</sub>                      | maximum current into output pins                                                                                                                                                                          |     | -100 to 100  | mA    |

| I <sub>CCI</sub>                    | maximum current into V <sub>CCI</sub> pin                                                                                                                                                                 |     | -100 to 100  | mA    |

| I <sub>CCP</sub>                    | maximum current into V <sub>CCP</sub> pin                                                                                                                                                                 |     | -100 to 420  | mA    |

| I <sub>VSS</sub>                    | maximum current out of VSS pin                                                                                                                                                                            |     | -420 to 100  | mA    |

| V <sub>ESD</sub>                    | ESD Voltage                                                                                                                                                                                               | HBM | > 4000       | V     |

| ¥ ESD                               | LSD Voltage                                                                                                                                                                                               | CDM | > 500        | V     |

| Тյ                                  | Operating junction temperature range                                                                                                                                                                      |     | -55 to +150  | °C    |

| T <sub>STG</sub>                    | Storage temperature range                                                                                                                                                                                 |     | -65 to +150  | °C    |

#### Table 2: Absolute Maximum Ratings

APIO16 DATASHEET

#### 4.2 RECOMMENDED OPERATING CONDITIONS

All recommended parameters below are specified across the entire operating temperature range unless otherwise specified.

#### Table 3: Recommended Operating Conditions

| SYMBOL             | PARAMETER                                                                                                                                                              | MIN | MAX              | UNITS |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-------|

| $V_{CCI}, V_{CCP}$ | supply voltages                                                                                                                                                        | 1.4 | 5.5              | V     |

| Vı                 | INTB, RESETB, MODE, A3_CSB2,P0_1, P0_2,<br>P0_3, P0_4, P0_5, P0_6, P0_7, P1_1, P1_2, P1_3,<br>P1_4, P1_5, P1_6, P1_7, A2/CSB1, A1/CSB0,<br>A0/MISO, SCL/SCLK, SDA/MOSI | 0   | 5.5              | V     |

| V <sub>o_I</sub>   | output voltage on serial interface pins                                                                                                                                | 0   | $V_{\text{CCI}}$ | V     |

| V <sub>O_P</sub>   | output voltage on port pins                                                                                                                                            | 0   | $V_{CCP}$        | V     |

| I <sub>OL</sub>    | LOW level output current on serial interface or port pins                                                                                                              | -   | 25               | mA    |

| I <sub>OH</sub>    | HIGH level output current on serial interface or port pins                                                                                                             | -   | -25              | mA    |

| I <sub>CCP</sub>   | Current into VCCP pin                                                                                                                                                  | -   | 410              | mA    |

| I <sub>VSS</sub>   | Current out of VSS pin                                                                                                                                                 | -   | -410             | mA    |

#### Table 4: Thermal Information

| SYMBOL           | PARAMETER                              | MIN | ТҮР    | MAX  | UNITS |

|------------------|----------------------------------------|-----|--------|------|-------|

| Tj               | Operating junction temperature         | -55 | -      | +125 | °C    |

| R <sub>θJA</sub> | Junction to ambient thermal resistance | -   | 70 TBD | -    | °C/W  |

| C.C.L.L.C. |

|------------|

| SEMICT     |

UCTOR

**API016**

DATASHEET

#### 4.3 ELECTRICAL CHARACTERISTICS

All parameters are specified across the entire operating temperature range and entire recommended operating range unless otherwise specified.

| Table 5: Ele                       | ctrical Characteristics: general |     |    |

|------------------------------------|----------------------------------|-----|----|

| PARAMETER                          | CONDITIONS                       | MIN | T١ |

| / <sub>cci</sub> POR start voltage |                                  | -   | 1. |

| CCP POR start voltage              |                                  | -   | 1. |

| SYMBOL                 | PARAMETER                                     | CONDITIONS                            | MIN   | TYP  | MAX  | UNITS |

|------------------------|-----------------------------------------------|---------------------------------------|-------|------|------|-------|

| V <sub>CCI_START</sub> | V <sub>CCI</sub> POR start voltage            |                                       | -     | 1.13 | 1.36 | V     |

| V <sub>CCP_START</sub> | V <sub>CCP</sub> POR start voltage            |                                       | -     | 1.13 | 1.36 | V     |

| V <sub>CCI_STOP</sub>  | V <sub>CCI</sub> POR stop voltage             |                                       | 0.8   | 1.08 | -    | V     |

| V <sub>CCP_STOP</sub>  | V <sub>CCP</sub> POR stop voltage             |                                       | 0.8   | 1.08 | -    | V     |

| V <sub>CCI_HYST</sub>  | V <sub>CCI</sub> POR hysteresis               |                                       | 25    | 52   | 110  | mV    |

| V <sub>CCP_HYST</sub>  | V <sub>CCP</sub> POR hysteresis               |                                       | 25    | 52   | 110  | mV    |

|                        | SDA/MOSI, SCL/SCLK, A0,                       | V <sub>CCI</sub> = 5.5V               | 1.65  | 2.43 | 2.7  |       |

| V <sub>IL_I</sub>      | A1/CSB0, A2/CSB1,                             | V <sub>CCI</sub> = 3.0V               | 0.9   | 1.3  | 1.5  | V     |

|                        | A3/CSB2, MODE, RESETB<br>pin low level input  | V <sub>CCI</sub> = 1.65V              | 0.495 | 0.68 | 0.83 |       |

|                        | voltage                                       | V <sub>CCI</sub> = 1.4V, 0°C to 110°C | 0.42  | 0.56 | 0.7  |       |

|                        | SDA/MOSI, SCL/SCLK, A0,                       | V <sub>CCI</sub> = 5.5V               | 2.65  | 2.86 | 3.85 |       |

| V <sub>IH_I</sub>      | A1/CSB0, A2/CSB1,                             | V <sub>CCI</sub> = 3.0V               | 1.45  | 1.62 | 2.1  | V     |

|                        | A3/CSB2, MODE, RESETB<br>pin high level input | V <sub>CCI</sub> = 1.65V              | 0.84  | 0.97 | 1.15 |       |

|                        | voltage                                       | V <sub>CCI</sub> = 1.4V, 0°C to 110°C | 0.75  | 0.85 | 0.98 |       |

|                        | SDA/MOSI, SCL/SCLK, A0,                       | V <sub>CCI</sub> = 5.5V               | 0.3   | 0.44 | 0.6  |       |

| V <sub>I_HYS_I</sub>   | A1/CSB0, A2/CSB1,                             | V <sub>CCI</sub> = 3.0V               | 0.22  | 0.32 | 0.46 | V     |

|                        | A3/CSB2, MODE, RESETB<br>pin input hysteresis | V <sub>CCI</sub> = 1.65V              | 0.15  | 0.29 | 0.45 |       |

|                        | pin input hysteresis                          | V <sub>CCI</sub> = 1.4V, 0°C to 110°C | 0.15  | 0.29 | 0.4  |       |

|                        |                                               | V <sub>CCP</sub> = 5.5V               | 1.65  | 2.43 | 2.7  |       |

| V <sub>IL_P</sub>      | port pin low level input<br>voltage           | V <sub>CCP</sub> = 3.0V               | 0.9   | 1.3  | 1.5  | V     |

|                        | voltage                                       | V <sub>CCP</sub> = 1.65V              | 0.495 | 0.68 | 0.83 |       |

|                        |                                               | V <sub>CCP</sub> = 1.4V, 0°C to 110°C | 0.42  | 0.56 | 0.7  |       |

|                        |                                               | V <sub>CCP</sub> = 5.5V               | 2.65  | 2.86 | 3.85 |       |

| V <sub>IH_P</sub>      | port pin high level input<br>voltage          | V <sub>CCP</sub> = 3.0V               | 1.45  | 1.62 | 2.1  | V     |

|                        | vollage                                       | V <sub>CCP</sub> = 1.65V              | 0.84  | 0.97 | 1.15 |       |

|                        |                                               | V <sub>CCP</sub> = 1.4V, 0°C to 110°C | 0.75  | 0.85 | 0.98 |       |

|                        |                                               | V <sub>CCP</sub> = 5.5V               | 0.3   | 0.44 | 0.6  |       |

| V <sub>I_HYS_P</sub>   | port pin input hysteresis                     | V <sub>CCP</sub> = 3.0V               | 0.22  | 0.32 | 0.46 | V     |

|                        |                                               | V <sub>CCP</sub> = 1.65V              | 0.15  | 0.29 | 0.45 |       |

|                        |                                               | V <sub>CCP</sub> = 1.4V, 0°C to 110°C | 0.15  | 0.29 | 0.4  | 1     |

| Table 0. Electrical characteristics, general | Table 6 | : Electrical | Characteristics: general |

|----------------------------------------------|---------|--------------|--------------------------|

|----------------------------------------------|---------|--------------|--------------------------|

| SYMBOL            | PARAMETER                       | CONDITIONS                                                         | MIN  | TYP  | MAX  | UNITS |

|-------------------|---------------------------------|--------------------------------------------------------------------|------|------|------|-------|

|                   | port pin output high            | V <sub>CCP</sub> = 5.5V, I <sub>OH_P</sub> = -25mA                 | 4.9  | 5.0  | -    |       |

|                   | voltage                         | V <sub>CCP</sub> = 3.0V, I <sub>OH_P</sub> = -25mA                 | 2.15 | 2.4  | -    |       |

|                   | i ottage                        | V <sub>CCP</sub> = 5.5V, I <sub>OH_P</sub> = -10mA                 | 5.25 | 5.3  | -    |       |

| V <sub>OH_P</sub> |                                 | V <sub>CCP</sub> = 3.0V, I <sub>OH_P</sub> = -10mA                 | 2.65 | 2.75 | -    | V     |

|                   |                                 | V <sub>CCP</sub> = 1.65V, I <sub>OH_P</sub> = -10mA                | 1.05 | 1.30 | -    |       |

|                   |                                 | V <sub>CCP</sub> = 1.4V, I <sub>OH_P</sub> = -4mA, 0°C to<br>110°C | 1.16 | 1.22 | -    |       |

|                   | and all contact loss.           | V <sub>CCP</sub> = 5.5V, I <sub>OL_P</sub> = 25mA                  | -    | 0.32 | 0.45 |       |

|                   | port pin output low<br>voltage  | V <sub>CCP</sub> = 3.0V, I <sub>OL_P</sub> = 25mA                  | -    | 0.42 | 0.68 |       |

|                   | voltage                         | V <sub>CCP</sub> = 5.5V, I <sub>OL_P</sub> = 10mA                  | -    | 0.13 | 0.18 |       |

| V <sub>OL_P</sub> |                                 | V <sub>CCP</sub> = 3.0V, I <sub>OL_P</sub> = 10mA                  | -    | 0.16 | 0.25 | V     |

|                   |                                 | V <sub>CCP</sub> = 1.65V, I <sub>OL_P</sub> = 10mA                 | -    | 0.28 | 0.51 |       |

|                   |                                 | V <sub>CCP</sub> = 1.4V, I <sub>OL_P</sub> = 4mA, 0°C to<br>110°C  | -    | 0.14 | 0.22 |       |

|                   |                                 | V <sub>CCI</sub> = 5.5V, I <sub>OH_I</sub> = -25mA                 | 4.9  | 5.0  | -    |       |

|                   | MISO pin output high<br>voltage | V <sub>CCI</sub> = 3.0V, I <sub>OH_I</sub> = -25mA                 | 2.15 | 2.4  | -    |       |

|                   | voltage                         | V <sub>CCI</sub> = 5.5V, I <sub>OH_I</sub> = -10mA                 | 5.25 | 5.3  | -    |       |

| V <sub>OH_I</sub> |                                 | V <sub>CCI</sub> = 3.0V, I <sub>OH_I</sub> = -10mA                 | 2.65 | 2.75 | -    | V     |

|                   |                                 | V <sub>CCI</sub> = 1.65V, I <sub>OH_I</sub> = -10mA                | 1.05 | 1.3  | -    |       |

|                   |                                 | V <sub>CCI</sub> = 1.4V, I <sub>OH_I</sub> = -4mA, 0°C to<br>110°C | 1.16 | 1.22 | -    |       |

|                   |                                 | V <sub>CCI</sub> = 5.5V, I <sub>OL_I</sub> = 25mA                  | -    | 0.32 | 0.45 |       |

|                   | INTB, MISO, SDA pin             | $V_{CCI} = 3.0V, I_{OL I} = 25mA$                                  | -    | 0.42 | 0.68 |       |

|                   | output low voltage              | V <sub>CCI</sub> = 5.5V, I <sub>OL I</sub> = 10mA                  | -    | 0.13 | 0.18 |       |

| V <sub>OL_I</sub> |                                 | V <sub>CCI</sub> = 3.0V, I <sub>OL I</sub> = 10mA                  | -    | 0.16 | 0.25 | V     |

|                   |                                 | V <sub>CCI</sub> = 1.65V, I <sub>OL_I</sub> = 10mA                 | -    | 0.28 | 0.51 |       |

|                   |                                 | V <sub>CCI</sub> = 1.4V, I <sub>OL_I</sub> = 4mA, 0°C to<br>110°C  | -    | 0.14 | 0.22 |       |

|                   |                                 | V <sub>CCP</sub> = 5.5V, V <sub>OH_P</sub> = 5.1V                  | -    | -21  | -16  |       |

|                   | port pin output high<br>current | V <sub>CCP</sub> = 3.0V, V <sub>OH_P</sub> = 2.6V                  | -    | -17  | -12  |       |

|                   | current                         | V <sub>CCP</sub> = 1.65V, V <sub>OH_P</sub> = 1.25V                | -    | -11  | -6   | mA    |

| I <sub>OH_P</sub> |                                 | V <sub>CCP</sub> = 1.4V, V <sub>OH_P</sub> = 1V, 0°C to<br>110°C   | -    | -9   | -4   |       |

|                   |                                 | V <sub>CCP</sub> = 5.5V, V <sub>OL_P</sub> = 0.4V                  | 22   | 31   | -    |       |

|                   | port pin output low<br>current  | V <sub>CCP</sub> = 3.0V, V <sub>OL_P</sub> = 0.4V                  | 15   | 24   | -    |       |

|                   | current                         | V <sub>CCP</sub> = 1.65V, V <sub>OL P</sub> = 0.4V                 | 7    | 13   | -    | mA    |

| I <sub>OL_P</sub> |                                 | 5                                                                  | 10   | -    |      |       |

| SYMBOL               | PARAMETER                                                            | CONDITIONS                                                                          | MIN | TYP | MAX  | UNITS |

|----------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|------|-------|

|                      | MICO nin autout high                                                 | V <sub>CCI</sub> = 5.5V, V <sub>OH_I</sub> = 5.1V                                   | -   | -21 | -16  |       |

|                      | MISO pin output high<br>current                                      | V <sub>CCI</sub> = 3.0V, V <sub>OH_I</sub> = 2.6V                                   | -   | -17 | -12  |       |

|                      | carrent                                                              | V <sub>CCI</sub> = 1.65V, V <sub>OH_I</sub> = 1.25V                                 | -   | -11 | -6   | mA    |

| I <sub>OH_I</sub>    |                                                                      | V <sub>CCI</sub> = 1.4V, V <sub>OH_I</sub> = 1V, 0°C to 110°C                       | -   | -9  | -4   |       |

|                      | INTB, MISO, SDA pin                                                  | V <sub>CCI</sub> = 5.5V, V <sub>OL_I</sub> = 0.4V                                   | 25  | 50  | -    |       |

|                      | output low current                                                   | V <sub>CCI</sub> = 3.0V, V <sub>OL_1</sub> = 0.4V                                   | 20  | 37  | -    |       |

|                      |                                                                      | V <sub>CCI</sub> = 1.65V, V <sub>OL_I</sub> = 0.4V                                  | 8   | 19  | -    | mA    |

| I <sub>OL_I</sub>    |                                                                      | V <sub>CCI</sub> = 1.4V, V <sub>OL_I</sub> = 0.4, 0°C to<br>110°C                   | 6   | 14  | -    |       |

| I <sub>VCCI_Q</sub>  | quiescent supply current into<br>V <sub>CCI</sub>                    | V <sub>CCI</sub> = 5.5V, all ports inputs tied to<br>VSS or 5.5V, no communications | -   | 220 | 300  | uA    |

| I <sub>VCCP_Q</sub>  | quiescent supply current into<br>V <sub>CCP</sub>                    | V <sub>CCP</sub> = 5.5V, all ports inputs tied<br>to VSS or 5.5V                    | -   | 30  | 50   | uA    |

| C <sub>IP</sub>      | port pin capacitance when port<br>configured as input <sup>(1)</sup> |                                                                                     | -   | TBD | -    | pF    |

| t <sub>v_intb</sub>  | Time from change on input port<br>to INTB valid                      |                                                                                     | 500 | -   | 1200 | ns    |

| t <sub>reset_w</sub> | required RESETB pulse width                                          |                                                                                     | 200 | -   | -    | ns    |

| t <sub>reset_r</sub> | recovery from RESETB                                                 |                                                                                     | 200 | -   | -    | ns    |

| t <sub>reset_a</sub> | time for RESETB to affect ports                                      | -                                                                                   | -   | -   | 200  | ns    |

#### Table 7: Electrical Characteristics: general

<sup>(1)</sup> not tested in production

Table 8: Electrical Characteristics: I<sup>2</sup>C/SMBUS operation

| SYMBOL                    | PARAMETER                                                  | CONDITIONS                                                      | MIN | TYP | MAX  | UNITS |

|---------------------------|------------------------------------------------------------|-----------------------------------------------------------------|-----|-----|------|-------|

| I                         | Input leakage on RESETB,<br>A3,A2,A1,A0                    | V <sub>I</sub> =5.5V or VSS                                     | -1  | -   | 1    | uA    |

| I <sub>OL_SDA</sub>       | I <sup>2</sup> C SDA pin low level sink<br>current         | V <sub>SDA</sub> =0.4V, V <sub>CCI</sub> =3.0V                  | 20  | 37  | -    | mA    |

| I <sub>OL_SDA</sub>       | I <sup>2</sup> C SDA pin low level sink<br>current         | V <sub>SDA</sub> =0.4V, V <sub>CCI</sub> =1.65V                 | 8   | 19  | -    | mA    |

| I <sub>OL_SDA</sub>       | I <sup>2</sup> C SDA pin low level sink<br>current         | V <sub>SDA</sub> =0.4V, V <sub>CCI</sub> =1.4V, 0°C to<br>110°C | 6   | 14  | -    | mA    |

| CI                        | SCL, SDA input capacitance <sup>(1)</sup>                  |                                                                 | -   | TBD | TBD  | pF    |

| f <sub>SCL</sub>          | SCL clock frequency                                        | V <sub>CCI</sub> =3.0                                           | -   | -   | 1000 | kHz   |

| f <sub>SCL</sub>          | SCL clock frequency                                        | V <sub>CCI</sub> =1.65V                                         | -   | -   | 400  | kHz   |

| f <sub>SCL</sub>          | SCL clock frequency                                        | V <sub>CCI</sub> =1.4V, 0°C to 110°C                            | -   | -   | 100  | kHz   |

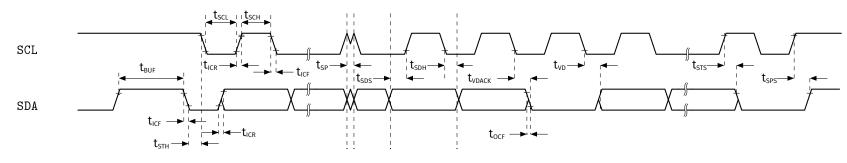

| t <sub>SCH</sub>          | SCL high time                                              |                                                                 | 260 | -   | -    | ns    |

| t <sub>SCL</sub>          | SCL low time                                               |                                                                 | 500 | -   | -    | ns    |

| t <sub>SP</sub>           | SCL, SDA maximum width of spike suppressed by input filter |                                                                 | 50  | -   | 200  | ns    |

| t <sub>SDS_I2C</sub>      | Data setup time                                            | V <sub>CCI</sub> =3.0                                           | 50  | -   | -    | ns    |

| t <sub>SDS_I2C</sub>      | Data setup time                                            | V <sub>CCI</sub> =1.65                                          | 100 | -   | -    | ns    |

| t <sub>SDS_I2C</sub>      | Data setup time                                            | V <sub>CCI</sub> =1.4V, 0°C to 110°C                            | 250 | -   | -    | ns    |

| t <sub>SDH_I2C</sub>      | Data hold time                                             |                                                                 | 0   | -   | -    | ns    |

| t <sub>ICR_I2C</sub>      | Input rise time                                            |                                                                 | -   | -   | 120  | ns    |

| t <sub>ICF_I2C</sub>      | Input fall time                                            |                                                                 | -   | -   | 120  | ns    |

| t <sub>OCF_I2C</sub>      | Output fall time                                           |                                                                 | -   | -   | TBD  | ns    |

| t <sub>BUF</sub>          | Bus free time between stop<br>and start                    |                                                                 | -   | -   | 500  | ns    |

| t <sub>sts</sub>          | Start or repeated start setup<br>time                      |                                                                 | -   | -   | 260  | ns    |

| t <sub>stH</sub>          | Start or repeated start hold<br>time                       |                                                                 | -   | -   | 260  | ns    |

| t <sub>SPS</sub>          | Stop setup time                                            |                                                                 | -   | -   | 260  | ns    |

| t <sub>VD</sub>           | SCL low to valid data                                      |                                                                 | -   | -   | 450  | ns    |

| t <sub>VDACK</sub>        | SCL low to valid ACK                                       |                                                                 | -   | -   | 450  | ns    |

| t <sub>rst_intb_i2c</sub> | Read of input port to INTB valid                           |                                                                 | 500 | -   | 1200 | ns    |

| t <sub>vq_I2C</sub>       | Write of output port to port<br>valid                      |                                                                 | 70  | -   | 200  | ns    |

| t <sub>sudp_i2c</sub>     | Setup data on port before read                             |                                                                 | TBD | -   | TBD  | ns    |

| t <sub>HDP_I2C</sub>      | Hold data on port after read                               |                                                                 | TBD | -   | TBD  | ns    |

<sup>(1)</sup> not tested in production

**SYMBOL**

t<sub>DIS\_MOSI</sub>

PARAMETER

UNITS

#### SCLK clock frequency V<sub>CCI</sub>= 3.0V MHz **f**<sub>SCLK</sub> \_ \_ 25 **f**<sub>SCLK</sub> SCLK clock frequency V<sub>CCI</sub> = 1.65V 10 MHz --V<sub>CCI</sub>=1.4V, 0°C to 110°C 2 MHz **f**<sub>SCLK</sub> SCLK clock frequency -clock high time TBD15 ns t<sub>HIGH</sub> clock low time TBD15 t<sub>LOW</sub> \_ ns CSBx setup time before first TBD50 \_ ns $t_{SU_{CSB}}$ \_ SCLK rising edge CSBx hold time after last TBD50 t<sub>H\_CSB</sub> \_ \_ ns SCLK falling edge data setup time for SPI TBD50 t<sub>su\_dat\_spi</sub> \_ \_ ns interface data hold time for SPI 0 \_ \_ ns t<sub>HD\_DAT\_SPI</sub> interface Time from read of input TBD500 TBD1000 ns t<sub>RST\_INTB\_SPI</sub> port to INTB valid Time from write of output TBD \_ TBD ns t<sub>v q spi</sub> port to port valid setup time for data on port TBD \_ TBD ns t<sub>SU\_DP\_SPI</sub> before read from port hold time for data on port TBD TBD \_ ns t<sub>H\_DP\_SPI</sub> after read from port time from falling edge of $V_{CCI} = 3.0V$ TBD TBD \_ t<sub>VD\_SPI</sub> ns SCLK to valid data on MISO time from falling edge of $V_{CCI} = 1.65V$ TBD TBD t<sub>VD\_SPI</sub> \_ ns SCLK to valid data on MISO V<sub>CCI</sub>=1.4V, 0°C to 110°C time from falling edge of TBD TBD t<sub>VD\_SPI</sub> \_ ns SCLK to valid data on MISO time from CSBx rising to $V_{CCI} = 3.0V$ 5 t<sub>DIS MOSI</sub> \_ 30 ns high impedance on MISO time from CSBx rising to $V_{CCI} = 1.65V$ \_ \_ 40 ns t<sub>DIS\_MOSI</sub> high impedance on MISO

V<sub>CCI</sub>=1.4V, 0°C to 110°C

#### Table 9: Electrical Characteristics: SPI operation

CONDITIONS

MIN

\_

TYP

MAX

time from CSBx rising to

high impedance on MISO

50

ns

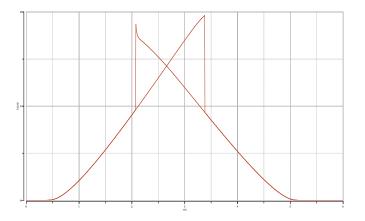

### **5 TYPICAL CHARACTERISTICS**

Include following typical curves here:

**API016**

DATASHEET

$I_{VCCL\_Q}$  Quiescent supply current into VCCI versus temperature

$I_{VCCP\_Q}$  Quiescent supply current into VCCP versus temperature

$V_{\text{CCP}}\text{-} V_{\text{OH}\_P}$  High level output voltage on port pin versus temperature

$V_{\text{OL}\_P}$  Low level output voltage on port pin versus temperature

Increase in  $I_{VCCP_Q}$  from single port pin swept from 0V to 5.5V with  $V_{CCI}$  = 5.5V (typical 27C)

**Rad-Hard I/O expander**

### **6 DETAILED DESCRIPTION**

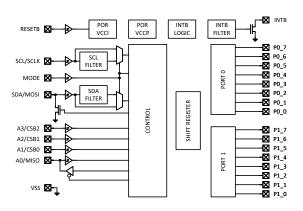

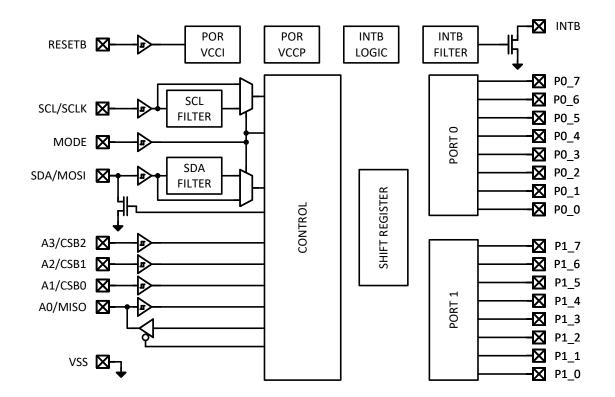

The APIO16 is a level translating I<sup>2</sup>C, SMBUS, SPI I/O expander. Please refer to the block diagram in Figure 2. The device incorporates a bi-directional serial bus and two 8-bit ports which can be controlled by and inspected by an external controller on the bus. The device can support two different types of serial bus: I<sup>2</sup>C and SPI bus. The type of bus used is set by tying the MODE pin to either VSS or VCCI. Each pin on each port can be individually programmed to be enabled as an output or disabled. When enabled as an output, the pin can drive high or low. At any time, the logic state on the pin can be read back via the serial interface. When the pins on the port are read, the state of the pins is saved in an internal register. If any of the pins configured as inputs changes from the value saved in the internal register, the INTB pin is pulled low, to alert the controller that the inputs have changed from the values last read on that port. Each of these functions is explained in more detail in the following sections.

### 6.1 FUNCTIONAL BLOCK DIAGRAM

#### Figure 1: block diagram

#### 6.2 POR VCCI

The device serial interface is powered through the VCCI pin.

There is a Power On Reset (POR) circuit which monitors the VCCI supply. If VCCI drops below **V**<sub>CCI\_STOP</sub> all internal registers are reset to initial conditions. The ports are reset to inputs only. The device cannot be programmed until VCCI is raised above **V**<sub>CCI\_START</sub> and RESETB is high.

The APIO16 posesses proprietary cold sparing circuitry on all inputs and outputs, for both the port pins and the serial interface pins. If the VCCI POR detects a low supply voltage on VCCI, all inputs and outputs become high impedance and can be driven by other devices connected to the same pins without exhibiting leakage. This allows the device to be used to construct "Cold Spareable" systems.

#### 6.3 RESETB

If the RESETB pin is pulled low, the serial interface is cleared, all internal registers are reset to initial conditions. The ports are reset to inputs only. The effect is identical to POR VCCI. If the POR VCCI has already been released by VCCI raising above **V**<sub>CCI\_START</sub> then the device will be capable of being programmed as soon as RESETB is raised to a high level, otherwise the device will wait until VCCI has been raised above **V**<sub>CCI\_START</sub>. If RESETB functionality is not desired, tie the RESETB pin to VCCI.

### 6.4 POR VCCP

The device ports are powered through the VCCP pin. There is a Power On Reset (POR) circuit which monitors the VCCP supply. If VCCP drops below  $V_{CCP\_STOP}$  the ports go high impedance and are suitable for cold-sparing applications. In this condition, the serial interface sees all the inputs as being in the low state. If the ports have previously been read and previously had a different state to all pins being low, this will cause INTB to be pulled low (see section on INTB operation). If the ports are read, they will read as being "all low".

The VCCP POR being asserted does NOT clear the internal state of the serial interface to its power on reset condition, this means that once the VCCP is restored to a voltage above  $V_{CCP\_START}$ , the ports assume the states controlled by the serial interface state. Consequently the APIO16 can be configured even with the VCCP supply pulled low, but the ports are not active until VCCP is raised.

#### 6.5 MODE

The MODE pin controls whether the part functions with an I<sup>2</sup>C interface (MODE pulled low) or an SPI interface (MODE pulled high). The MODE pin is not latched in the IC. It is recommended that the MODE pin be tied high (to VCCI) or low (to VSS), so that its state is stable when the IC powers up and is released from RESETB and it is recommended that the MODE pin is not changed during operation.

#### 6.6 PORTS

There are two 8-bit ports: Port 0 and Port 1. All of the pins in an individual port can be configured, read or written at the same time. The power supply for the ports is VCCP, which is independent of the power supply for the serial interface: VCCI.

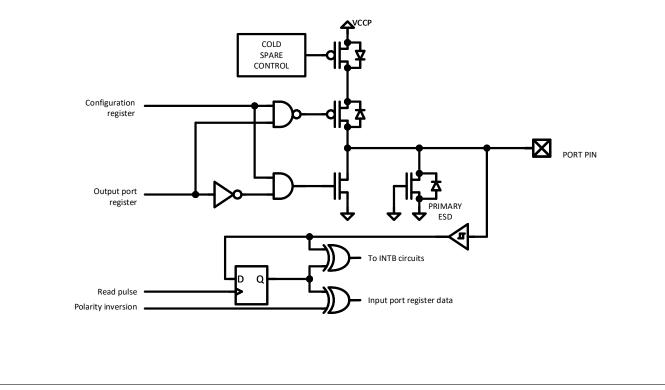

Within each port, each bit can be configured to be tri-state or driven and can be configured to drive high or low. In addition, the voltage on each port pin is converted to a logic value by a schmitt trigger. The resultant logic signal can be optionally inverted and the result can be read back by the controller. When driving the pin high, the pin is driven to the VCCP voltage. If the pin is configured to be tri-state, it can be driven externally to a voltage higher than the VCCP voltage up to the ABS MAX voltage of 5.5V without forward biasing any protection diodes and with no damage. If VCCP or VCCI are below their POR threshold, all port pins go into "high impedance" input state.

If the port pins are not lower than approximately 300mV above VSS or are not higher than approximately 300mV below VCCP, the internal Schmitt trigger circuits will cause some additional quiescent current to be drawn from the VCCP pin. Please see the typical characteristics plot of increase in Ivcc\_Q for a single port pin.

A simplified schematic of the circuitry within each port pin is shown in Figure 2

Figure 2: simplified port pin schematic

#### 6.7 INTB

**API016**

On a VCCI POR condition, or when RESETB is pulled low, the INTB pin goes high impedance, in addition two latches are cleared, indicating that neither port has been read since the last VCCI POR. When the ports are read, the current state of the port is stored in an internal register, in addition, the latch which stores whether the port has been read is set. The state of the pins on the port are continuously compared with the values in the register which stores the state of the inputs since the last read. If any of the inputs has a state different to the value last read AND the pin is configured to be an input AND the port that the input is a part of has been read since the last VCCI POR release, a signal is generated, which passes through a nominal 750ns filter. If the signal is present without changing for longer than the filter duration, the INTB pin will be pulled low, to indicate to the controller that one of the input pins has changed state.

If the changed pin goes back to its previous state OR the port that that pin is part of is read, the signal into the INTB filter is cleared. If it stays cleared for longer than the filter duration (750ns), then INTB will be set to a high impedance state again.

If the INTB pin functionality is not desired, it is recommended to tie INTB pin to VSS.

### 6.8 I<sup>2</sup>C OPERATION

If the MODE pin is pulled low, the part operates in I<sup>2</sup>C mode. In I<sup>2</sup>C mode, the APIO16 is SMBUS 3.2 compliant. In I<sup>2</sup>C operation the APIO16 operates as a target device. There is an external device, typically a microcontroller or FPGA that acts as the controller. Communication is initiated by and controlled by the controller. There are two communications lines: SDA and SCL, which are typically pulled up by resistors. Multiple devices can be connected to the same SDA and SCL lines. There must be at least one controller in addition to the one or more

### PRELIMINARY DATASHEET

**Rad-Hard I/O expander**

APIO16 devices, there may be other devices on the bus as well. Each target device on the bus has a device address. In the case of the APIO16, there is a range of 16 addresses that can be selected by hard wiring address pins. When the controller sends a command to a target device, it includes a target device address, to select which target device is to be addressed.

The SCL/SCLK pin functions as the SCL input pin in I<sup>2</sup>C. The SCL FILTER is used to filter out glitches on the SCL line, it is guaranteed that glitches less than 50ns will be suppressed.

The SDA/MOSI pin functions as the SDA bidirectional pin in I<sup>2</sup>C. The SDA FILTER is used to filter out glitches on the SDA line, it is guaranteed that glitches less than 50ns will be suppressed.

The A3/CSB2, A2/CSB1, A1/CSB0 and A0/MISO pins function as address pins A3, A2, A1 and A0 respectively. These pins select the I<sup>2</sup>C address used by the device.

The seven bit I<sup>2</sup>C device address selected by pulling the address pins high or low is listed in Table 10. Each I<sup>2</sup>C command contains a 7-bit device address (dad[6:0]). If the address in the I<sup>2</sup>C command matches the device address selected by the address pins on the device, the device will respond to the I<sup>2</sup>C command. Otherwise, the device will ignore the command.

| A  | DDRES | SS PII | NS | I <sup>2</sup> C ADDRESS |

|----|-------|--------|----|--------------------------|

| A3 | A2    | A1     | A0 | (HEX)                    |

| L  | L     | L      | L  | 20                       |

| L  | L     | L      | Н  | 21                       |

| L  | L     | Н      | L  | 22                       |

| L  | L     | Н      | Н  | 23                       |

| L  | Н     | L      | L  | 24                       |

| L  | Н     | L      | Н  | 25                       |

| L  | Н     | Н      | L  | 26                       |

| L  | Н     | Н      | Н  | 27                       |

| Н  | L     | L      | L  | 28                       |

| Н  | L     | L      | Н  | 29                       |

| Н  | L     | Н      | L  | 2A                       |

| Н  | L     | Н      | Н  | 2B                       |

| Н  | Н     | L      | L  | 2C                       |

| Н  | Н     | L      | Н  | 2D                       |

| Н  | Н     | Н      | L  | 2E                       |

| Н  | Н     | Н      | Н  | 2F                       |

#### Table 10: APIO16 I<sup>2</sup>C address

#### **API016** DATASHEET

PRELIMINARY DATASHEET

COPYRIGHT 2025 APOGEE SEMICONDUCTOR INC. DOC ID: 601-000-080-A04 (SUBMIT DOCUMENTATION FEEDBACK)

REVISED: 2025-FEB-06 18 / 35

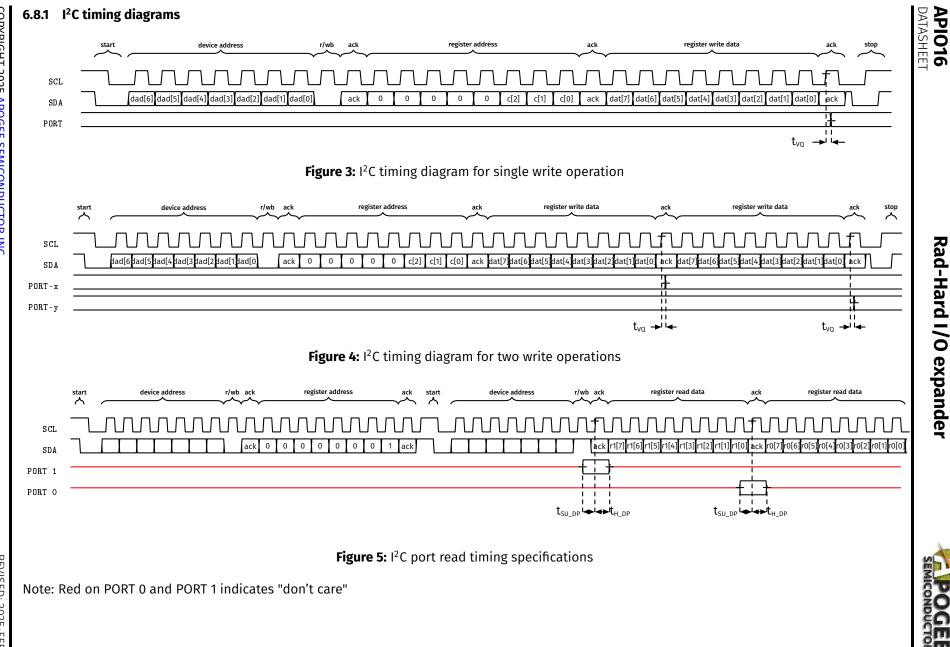

Figure 6: I<sup>2</sup>C timing specifications

#### 6.8.2 I<sup>2</sup>C write

In Fig 3 we see the timing for a single write to the device. First, there is a START symbol followed by the target device address, sent MSB first (dad[6:0]) and then the r/wb bit, which will be low, indicating a write operation. Next, the target device acknowledges that it saw a correct address, pulling the SDA line low (ack). Next, the register address is sent, which tells the target which register to write to (rad[7:0]). rad[7:3] must all be zero, rad[2:0] are bits C2, C1, C0 as detailed in the REGISTER DESCRIPTIONS section. Next, the target acknowledges that it saw a valid command, pulling the SDA line low (ack). Next, the data to be written to the selected register is sent to the target (dat[7:0]), Next, the target acknowledges that it saw 8 bits of data, pulling the SDA line low (ack). Finally, there is a STOP symbol.

When a register is written in this manner, the register bits take effect after time:  $t_{vQ}$  after the rising edge of SCL during the final ack after the register data has been received.

In Fig 4 we see the timing for two consecutive writes to the device. First, there is a START symbol, followed by the target device address (dad[6:0]) and the r/wb bit, which will be low, indicating a write operation. Next, the target device acknowledges that it saw a correct address, pulling the SDA line low (ack). Next, the command word is sent, which tells the target which register to write to (rad[7:0]). rad[7:3] must all be zero, rad[2:0] are bits C2, C1, C0 as detailled in the REGISTER DESCRIPTIONS section. Next, the target acknowledges that it saw a valid command, pulling the SDA line low (ack). Next, the data to be written to the selected register is sent to the target (dat[7:0]), Next, the target acknowledges that it saw 8 bits of data, pulling the SDA line low (ack). Next, the data to be written to the next register is sent to the target (dat[7:0]), Next, the target acknowledges that it saw 8 bits of data, pulling the SDA line low (ack). Finally, there is a STOP marked in red.

When there are multiple I<sup>2</sup>C writes without start conditions between them, consecutive writes address the same type of register, but for the other port.

Examples:

If the first write addresses register 2, the second will address register 3, the third register 2, the fourth, register 3 and so on.

If the first write addresses register 3, the second will address register 2, the third register 3, the fourth, register 2 and so on.

If the first write addresses register 5, the second will address register 4, the third register 5, the fourth, register 4 and so on.

#### 6.8.3 I<sup>2</sup>C read

The controller first must send the target **APIO16** address with r/wb bit sent to a logic "0" followed by the address of the register that it is desired to read. After the target ACK, the controller must send a repeated START condition (or a STOP followed by a START), followed by the target address once more and the r/wb bit set to a logic "1", the target will reply with an ACK. At this point, the controller must stop pulling SDA down , allowing the Target to send data back to the controller on the SDA line. As the SCL line is toggled by the controller, the target shifts out the read data, MSB first. At the end of the received byte, if the controller must provides an ACK to the target, the target will then provide another data word from the complimentary register as described in the below examples:

If the first register read is register 0, the second register read will be register 1, the third register 0, the fourth, register 1 and so on.

If the first register read is register 1, the second register read will be register 0, the third register 1, the fourth, register 0 and so on.

If the first register read is register 3, the second register read will be register 2, the third register 3, the fourth, register 2 and so on.

Rad-Hard I/O expander

There is no limit to the number of reads that can be performed. To terminate reads, the controller must fail to provide an ACK to acknowledge the last data byte read.

Note: the polarity of the r/wb used in  $I^2C$  is the opposite to the polarity used in SPI

#### 6.8.4 I<sup>2</sup>C read from port

In I<sup>2</sup>C mode, when reading from the port pins, the state of the port pins is latched shortly after the rising edge on SCL during the ACK just before the data is transferred from the target to the controller. To guarantee correctly latching the expected data on the pins, the data must be stable before and after that time, as shown in Figure 5

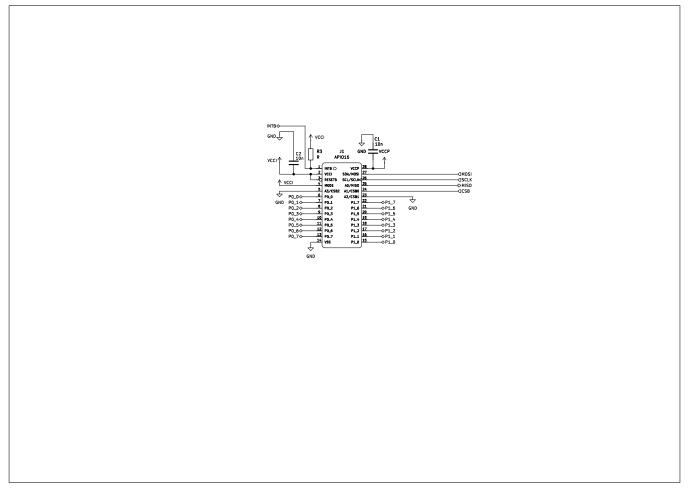

#### 6.9 SPI OPERATION

If the MODE pin is pulled high, the part operates in SPI mode. In SPI operation the **APIO16** operates as a target device. There is an external device, typically a microcontroller or FPGA that acts as the Controller. Communication is initiated by and controlled by the controller. There are two communications lines from Controller to Target device: MOSI and SCLK. Multiple devices can be connected to the same MOSI and SCLK lines. There must be at least one controller in addition to the one or more **APIO16** devices, there may be other devices on the bus as well. The SDA/MOSI pin functions as the MOSI data from controller to target input pin. There is no deglitching of signals on MOSI in SPI mode. The SCL/SCLK pin functions as the SCLK clock input pin in SPI. There is no deglitching of signals on SCLK in SPI mode.

Each target **APIO16** device on the bus is selected by the CSB0, CSB1, CSB2 lines. The A3/CSB2, A2/CSB1, and A1/CSB0 pins function as CSB2, CSB1 and CSB0 respectively. The IC will ignore data on MOSI unless all three of CSB0, CSB1 and CSB2 are low. CSBx is used in the following sections to represent the boolean logical function: CSBx = (CSB0 OR CSB1 OR CSB2), the statement: "CSBx is low" will be taken to mean that all three of CSB0, CSB1 AND CSB2 are low simultaneously.

The A0/MISO pin functions as the tri-state output driver from the target to the controller. It is tri-state except when sending data back from target to controller.

Provided the VCCI is 3V or higher, the **APIO16** can support a maximum bus speed of 25MHz, provided all the timings required are met. Below 3V on VCCI, the **APIO16** can support a maximum bus speed of TBD 10 MHz.

> PRELIMINARY DATASHEET Rad-Hard I/O expander

POGEE

COPYRIGHT 2025 APOGEE SEMICONDUCTOR INC. DOC ID: 601-000-080-A04 (SUBMIT DOCUMENTATION FEEDBACK)

REVISED: 2025-FEB-06 22 / 35

#### 6.9.2 SPI write

Refer to Figure 7 To write to the **APIO16** in SPI mode, CSBx must be brought low, at least  $t_{SU\_CSB}$  before the first rising edge of SCLK. Data is clocked into the MOSI pin on the rising edge of SCLK. Data must be present  $t_{SU\_DAT\_SPI}$  before each rising edge of SCLK and be held for a minimum of  $t_{H\_DAT\_SPI}$  after the rising edge of SCLK. The first data bit clocked in is C[2], then C[1] then C[0], which selects the register address to be written to. Next is the w/rb bit which indicates whether a register is to be read or written. The w/rb bit must be high to write to a register (NOTE: This is the opposite polarity from that used in I<sup>2</sup>C mode ) The next bit MUST be a zero and the following three bits are "don't care" bits. The following eight bits are the eight bit value to be written to the selected register. The new register value takes effect after a time  $t_{VQ}$  after the falling edge of the clock that occurs after the rising edge that clocked in the last data bit: dat[0]. CSBx must remain low until at least  $t_{H\_CSB}$  after that falling edge.

CSBx can remain low after the last falling edge and a new address and data value can be clocked in: it is not mandatory to cycle CSBx after each byte written, however, it is recommended that CSBx IS cycled after each data byte written. Please see the section on error conditions.

#### 6.9.3 SPI read

Refer to Figure 9 In SPI mode, the A0/MISO pin is used as a MISO pin, providing data from the target to the controller. The MISO pin is tri-stated, except when it is required to send data back to the controller. To read from the **APIO16** in SPI mode, CSBx must be brought low, at least  $t_{SU\_CSB}$  before the first rising edge of SCLK. Data is clocked into the MOSI pin on the rising edge of SCLK. Data must be present  $t_{SU\_DAT\_SPI}$  before each rising edge of SCLK and be held for a minimum of  $t_{H\_DAT\_SPI}$  after the rising edge of SCLK. The first data bit clocked in is C[2], then C[1] then C[0], which selects the register address to be read from. Next is the w/rb bit which indicates whether a register is to be read or written. The w/rb bit must be low to read from a register. The next bit MUST be a zero and the following three bits are "don't care" bits. Next, the target changes the MISO pin from high impedance to actively drive data onto the MISO line at a time  $t_{VD\_SPI}$  after the next falling edge on SCLK. The desired eight bits of data to be read back is clocked out onto the MISO line, with data changing  $t_{VD\_SPI}$  after the falling edge at the end of the last data bit on MISO, or  $t_{DIS\_MOSI}$  after CSBx goes high. CSBx can remain low after the last falling edge and a new address and data value can be clocked in: it is not mandatory to cycle CSBx after each byte written, however, it is recommended that CSBx IS cycled after each data byte written.

Note: the polarity of the w/rb used in SPI is the opposite to the polarity used in  $I^2C$

#### 6.9.4 SPI read 4-wire

Multiple **APIO16** devices can be connected to the same MISO line. As long as only ONE **APIO16** device is requested to send back data at a time, there will be no bus conflicts on the MISO line. It is recommended to connect a pull up or pull down resistor onto the MISO line, to ensure that it does not float when no devices are addressed.

#### 6.9.5 SPI read 3-wire

It is also possible to short the MISO and MOSI pins together and connect multiple devices to the same wire, provided both of the following conditions are met:

- Only ONE APIO16 device is requested to send back data at a time.

- The controller tri-states its output driving the joined MISO/MOSI line at the appropriate time to ensure the controller and Target are not both driving the same line at the same time.

#### 6.9.6 SPI read from port

In SPI mode, when reading from the port pins, the state of the port pins is latched on the 3rd rising SCLK edge after the w/rb bit is latched. To guarantee correctly latching the expected data on the pins, the data must be stable  $t_{SU_DP_SPI}$  before and remain stable  $t_{H_DP_SPI}$  after that clock edge.

#### 6.10 REGISTER DESCRIPTIONS

In I<sup>2</sup>C and in SPI mode, the internal register functionality is identical.

There are eight register addresses, as shown in Table 11. All eight registers can be read from, six of the registers can be read or written. Registers 0 and 1 can only be read.

| BIT | NAM | E(S) | REGISTER | REGISTER             | PROTOCOL   | RESET     |

|-----|-----|------|----------|----------------------|------------|-----------|

| C2  | C1  | C0   | NUMBER   |                      |            | DEFAULT   |

| 0   | 0   | 0    | 0        | Input port 0         | read       | XXXX XXXX |

| 0   | 0   | 1    | 1        | Input port 1         | read       | XXXX XXXX |

| 0   | 1   | 0    | 2        | Output port 0        | read/write | 1111 1111 |

| 0   | 1   | 1    | 3        | Output port 1        | read/write | 1111 1111 |

| 1   | 0   | 0    | 4        | Polarity port 0      | read/write | 0000 0000 |

| 1   | 0   | 1    | 5        | Polarity port 1      | read/write | 0000 0000 |

| 1   | 1   | 0    | 6        | Configuration port 0 | read/write | 1111 1111 |

| 1   | 1   | 1    | 7        | Configuration port 1 | read/write | 1111 1111 |

#### Table 11: APIO16 registers

Reading register 0 returns the state of the pins on port 0. The MSB gives the state of P0\_7, the LSB gives the state of P0\_0. Reading register 1 returns the state of the pins on port 1. The MSB gives the state of P1\_7, the LSB gives the state of P1\_0. Writing to register 0 or register 1 has no effect.

#### **Table 12:** Input port 0 register (c[2:0] = 0)

| Bit      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Port Pin | P0_7 | P0_6 | P0_5 | P0_4 | P0_3 | P0_2 | P0_1 | P0_0 |

**Table 13:** Input port 1 register (c[2:0] = 1)

| Bit      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Port Pin | P1_7 | P1_6 | P1_5 | P1_4 | P1_3 | P1_2 | P1_1 | P1_0 |

Register 2 controls the output data for port 0. A "1" in the port makes the port pull high if the output on that pin is enabled, a "0" makes the port pull low if the output on that pin is enabled. Asserting POR VCCI or pulling RESETB low clears the register to the default state of all "1"s, i.e. all pins will pull high if enabled. The MSB of the register affects port pin P0\_7, the LSB affects port pin P0\_0. Reading register 2 gives the current setting for register 2.

Register 3 controls the output data for port 1. A "1" in the port makes the port pull high if the output on that pin is enabled, a "0" makes the port pull low if the output on that pin is enabled. Asserting POR VCCI or pulling RESETB low clears the register to the default state of all "1"s, i.e. all pins will pull high if enabled. The MSB of the register affects port pin P1\_7, the LSB affects port pin P1\_0. Reading register 3 gives the current setting for register 3.

### PRELIMINARY DATASHEET

**Rad-Hard I/O expander**

APIO16 DATASHEET

**Table 14:** Output port 0 register (c[2:0] = 2)

| Bit      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Port Pin | P0_7 | P0_6 | P0_5 | P0_4 | P0_3 | P0_2 | P0_1 | P0_0 |

| Default  | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Table 15: Output port 1 register (c[2:0] = 3)

| Bit      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Port Pin | P1_7 | P1_6 | P1_5 | P1_4 | P1_3 | P1_2 | P1_1 | P0_0 |

| Default  | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Register 4 controls the polarity inversion for read of port 0. A "1" inverts the polarity of the bit which will be read back when register 0 is read. The MSB of the register affects the read for port pin P0\_7, the LSB affects the read for port pin P0\_0. Note that changing this bit does NOT affect the INTB state, it simply inverts or does not invert the polarity of bits read back when register 0 is read. Reading register 4 gives the current setting for register 4.

Table 16: Polarity port 0 register (c[2:0] = 4)

| Bit      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Port Pin | P0_7 | P0_6 | P0_5 | P0_4 | P0_3 | P0_2 | P0_1 | P0_0 |

| Default  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Register 5 controls the polarity inversion for read of port 1. A "1" inverts the polarity of the bit which will be read back when register 1 is read. The MSB of the register affects the read for port pin P1\_7, the LSB affects the read of port pin P1\_0. Note that changing this bit does NOT affect the INTB state, it simply inverts or does not invert the polarity of bits read back when register 1 is read. Reading register 5 gives the current setting for register 5.

**Table 17:** Polarity port 1 register (c[2:0] = 5)

| Bit      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Port Pin | P1_7 | P1_6 | P1_5 | P1_4 | P1_3 | P1_2 | P1_1 | P1_0 |

| Default  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Register 6 controls the output enables for port 0. A "1" in the port makes the port pin high impedance, a "0" enables the output on that pin. Asserting POR VCCI or pulling RESETB low clears the register to the default state of all "1"s, i.e. all pins are inputs. The MSB of the register affects port pin P0\_7, the LSB affects port pin P0\_0. Reading register 6 gives the current setting for register 6.

Table 18: Configuration port 0 register (c[2:0] = 6)

| Bit      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Port Pin | P0_7 | P0_6 | P0_5 | P0_4 | P0_3 | P0_2 | P0_1 | P0_0 |

| Default  | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Register 7 controls the output enables for port 1. A "1" in the port makes the port pin high impedance, a "0" enables the output on that pin. Asserting POR VCCI or pulling RESETB low clears the register to the default state of all "1"s, i.e. all pins are inputs. The MSB of the register affects port pin P1\_7, the LSB affects port pin P1\_0. Reading register 7 gives the current setting for register 7.

| <b>Table 19:</b> Configuration port 1 register (c[2:0] = 7) |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| Bit      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Port Pin | P1_7 | P1_6 | P1_5 | P1_4 | P1_3 | P1_2 | P1_1 | P1_0 |

| Default  | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

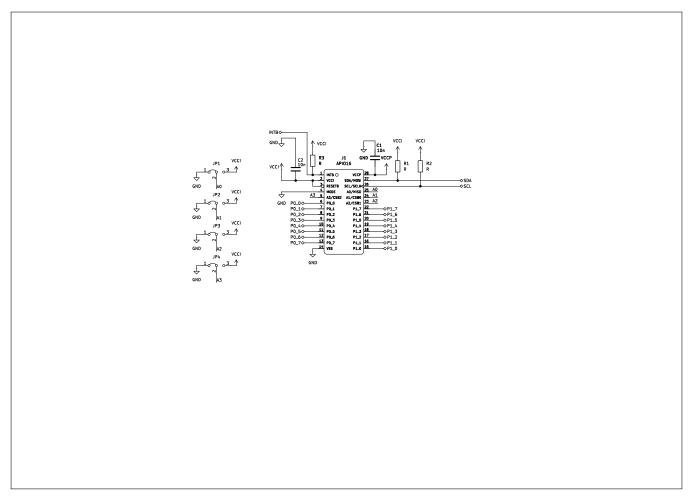

#### 6.11 APPLICATION CIRCUIT

#### 6.11.1 Basic I<sup>2</sup>C operation

Please see Figure 10. For basic l<sup>2</sup>C operation, all that is necessary is to tie the A0, A2, A2, A3 pins high or low to program the desired target device address.

Ensure that SDA and SCL are connected to the I<sup>2</sup>C bus and have appropriately sized pullup resistors somewhere on those lines. Decoupling capacitors of at least 10nF should be within 25mm of the IC.

It is recommended that INTB is pulled up or pulled down through a resistor, even if this signal is not used. It is also acceptable to tie INTB directly to the VSS of the device.

The port pins P0\_1 through P0\_7 and P1\_0 through P1\_7 are configurable to be inputs and/or outputs as desired. If used as inputs, it is recommended to ensure that those pins are always driven or have a pull-up or pull down resistor

#### Figure 10: basic I<sup>2</sup>C application

#### 6.11.2 I<sup>2</sup>C connection to FPGA low voltage bank

FPGA I/Os are grouped in banks, each bank can be tied to a different power supply. It is often the case that not all pins on a low voltage bank are used, there can be several pins un-used. Because the **APIO16** has level transation built in, it is possible to use these pins to control the **APIO16**. If the part is used in I<sup>2</sup>C mode, the SDA

**Rad-Hard I/O expander**

and SCL pins would be pulled up to the VCCI rail, but note that INTB could be pulled up to a different, higher voltage if needed. The **APIO16** can reliably support operation on VCCI and/or VCCP down to 1.4V.

#### 6.11.3 Sizing the pull-up resistors for SDA and SCLK for I<sup>2</sup>C